Well. I don’t want adams to win

Only Bayes Can Judge Me

Well. I don’t want adams to win

I can only offer my solidarity and sympathies. If I were still living in the US, I’d probably have started taking firearms training and bought some by now.

eric adams should change his platform to “I’m not cuomo”

Sure, but we should be calling these things out directly, rather than indirectly in a way that fuels racism.

Cuomo

A citation on page 28 includes ChatGPT in the cited web page URL.

What’s with this homie dissin’ my URL

some parrots are more stochastic than others

I checked the link, the thread elaborates a bit more:

to which my understanding is: this is absolutely true as well.

Hey, as long as we can learn from this, then we are doing our best to keep this bar nazi-free.

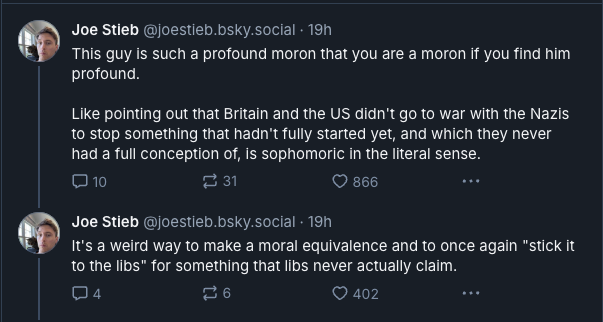

I think it’s accurate that the US and England didn’t join to stop the Holocaust. Sentence 3 is a little oversimplified, and sentence 4 is straight-up lunacy.

Yes, exactly. The same capitalist/colonialist/imperialist forces that exploit the global south are the same that want AI to automate everyone into abject poverty. We can do better and show class solidarity by not perpetuating these racist stereotypes.

Let’s drop the “indian” part of this and come up with something else, please.

Don’t look up who the president is, it might come as a shock /s

Making a startup named Sphinctr

You’re welcome!

Pre-watch: With the prior knowledge that her main job prior to this was wrestling promoter, the ol’ overtonussy is preeeetty loose

Post-watch: lol

New animation (1:20) by theforestjar about AI art.

Rupi Kaur

should sue

I don’t know that we can offer you a good world, or even one that will be around for all that much longer. But I hope we can offer you a good childhood. […]

When “The world is gonna end soon so let’s just rawdog from now on” gets real

How much of this is the AI bubble collapsing vs. Ohiophobia

Good ol’ rat mikes. (Rode-nt -> rodent)